伴随着5G通信技术的到来与越来越成熟的物联网(internet-of-things, IoT)技术的应用,人们对5G/IoT相关的集成电路芯片设计投来更加热切的目光。例如,数字电路的逻辑单元和存储器设计有什么不同? 5G相关的射频IP芯片设计有哪些? 对于IoT系统芯片如何实现低功耗要求? IP单元及信号接口单元的版图设计如何实现?

同时,云端大数据的数据流实时处理(real-time analytical processing)推动着高性能计算机芯片的研发;终端的存储一体化运算(in-memory computing,IMC)对新一代存储器单元设计有了更新的要求。无论是云端或是终端的芯片设计,当前与未来都要具有人工智能的机器学习功能,云端芯片更多地解决并提升深度学习中的“训练”(training)能力, 终端芯片则更多地解决并提升深度学习中的“推理”(inference)能力。

5G/IoT的专用集成电路的市场需求,云端终端的智能芯片发展要求,从架构到系统,包括电路设计与物理设计与版图设计项目,已经摆在了芯片设计团队的面前。这些设计包括了集成电路的标准设计、半定制设计和全定制设计。芯片制造商通常仅提供通用型单元库(generic library)因而IoT需要更多半定制、5G需要全定制的版图设计。

针对5G/IoT技术的迫切需求,本文介绍集成电路产业中版图设计技术的简要过程,从而讲述标准版图设计、半定制设计与全定制版图设计的应用,并以5G/IoT场合的高性能和高速数据率相关的IP进行简短的讨论,版图设计质量对最终系统的影响等。文末强调版图设计与系统芯片、MCU芯片与模拟和混合信号设计以及与射频芯片设计的紧密相关和依赖性,重点说明版图设计在集成电路产业中的重要角色。

1. 集成电路的版图设计方法

集成电路设计方法涉及面广,内容复杂,其中版图设计是集成电路物理实现的基础技术。版图设计的质量好坏直接会影响到集成电路的功耗、性能和面积。在系统芯片(system-on-chip, SoC)设计中,集成了接口单元(input/output,I/O),标准逻辑单元(standard cell),模拟与混合信号(analog mixed-signal, AMS)模块,存储器(memory,例如ROM,RAM)和多种IP模块。所有这些模块的物理实现,全都离不开基本的版图设计。

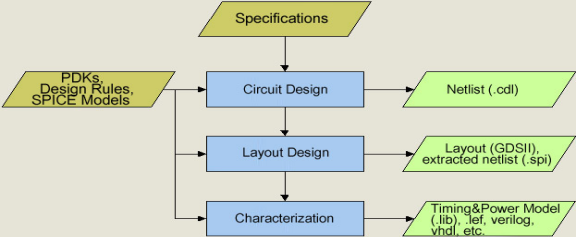

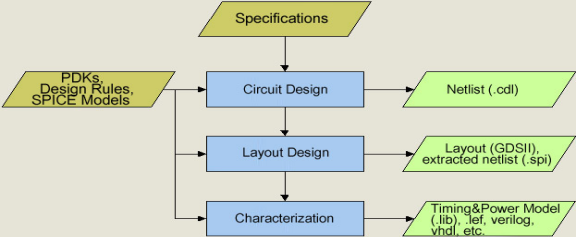

工程实践中,从定义系统芯片参数(specifications)完成后,人们常常将最常见的数字集成电路中标准逻辑单元的版图设计过程简化为电路设计(circuit design)、版图设计(layout design)和特征化(characterization)等三个步骤,见图1简化的版图设计流程图。在实践中,版图设计类型又分为: 1)标准版图设计,2)半定制版图设计,和3)全定制版图设计。

图1 集成电路版图设计的简化流程图

2.集成电路中的标准版图设计

标准版图设计通常用于数字集成电路的标准单元库、输入输出单元库等。存储器的版图设计属于半定制版图设计,它的存储单元(例如RAM cell)的版图采用标准单元库的设计方法,其余部分则为不规则的版图设计。模拟与混合信号(analog mixed-signal, AMS)的版图设计以及射频电路的版图设计则属于全定制的版图设计。

标准单元库中包括两大类单元:(1)组合逻辑(combinational)单元,例如反向器与非门、选择器等。(2)时序逻辑(sequential)单元,例如寄存器、锁存器、存储器等。

对于数字电路中的标准单元设计,是从布尔逻辑(Boolean logic)描述并定义单元的逻辑关系开始,接着是电路设计(schematic capture或circuit design)与电路仿真(circuit simulation),而后开始版图设计。版图设计需要符合制造工艺规则检查(design rule check,DRC)和版图电路一致性检查(layout versus schematic,LVS)通过才算完成,这时,版图设计的结果用“图形显示系统第二版”(graphic display system II,GDSII)文件记载,并作为芯片制造中制作掩模板(mask)的依据。数字电路的标准单元和I/O单元完成版图设计后,还要做寄生参数(电阻R电容C)提取(parasitic extraction,RCX),供电路设计者作进一步拟合优化处理,这种反标方法(back-annotation)也是芯片级设计的重要步骤之一。图2给出了比较完整的版图设计全流程图。

图2 集成电路版图设计的全流程图

从标准单元和I/O单元的版图设计结果,需要产生物理信息和时序信息供芯片物理设计布局布线(place & route,P&R)使用。物理信息以单元库交换格式(library exchange format,LEF)文件表达,它是在相应的GDSII文件的基础上,“忽略”底层信息,仅仅保留并提取金属1层(metal 1,M1)以及更上层的多边形(polygon)数据作为P&R使用,这样就会极大地加快P&R的运行速度,缩短时序收敛时间。例如,对于存储器版图的LEF文件,会使用到M1,M2甚至M3的信息。

图3 集成电路标准版图设计中标准单元具有同等高度与不同宽度

对于标准单元的版图,根据工艺要求,标准逻辑单元的高度是固定的,宽度为最小单元宽度的公约数倍数,例如在图3中,左图为反向器(inverter,INV)的版图,中图为选择器(multiplexer,MUX)的版图,右图为D型寄存器的(D-Flip Flop, DFF)的版图。如上所述,从版图设计中,可以导出并建立GDSII和LEF文件。GDSII文件经过设计签核(design sign-off)过程由代工厂使用于芯片制造,LEF文件用于全芯片的P&R物理设计。

标准单元的时序信息过去曾经以时序库单元格式(timing library format,TLF)文件表达,目前以自由时序库单元格式(liberty,“.lib”)文件表达。产生时序库文件需要根据制造工艺调用SPICE模型,比如最常用的BISM4模型;根据制造工艺参数,进行库单元时序仿真,例如Hspice和Spectre仿真器。

从相应的GDSII文件中,根据半导体器件物理基础参数,提取单元电路的输入输出负载(CL),提取其静态功耗和动态功耗数据,建立一套数据库,在做功耗分析和低功耗设计时使用。CMOS的总功耗 Ptotal= Pstatic + Pdynamic,静态功耗Pstatic与工艺参数相关,而动态功耗Pdynamic与CL相关。因此,在做各种版图设计时,应当尽量减小输入输出端的电容,从而提高库单元速度即芯片的性能。

另一方面,对于180nm或者更加先进的工艺,信号完整性(signal integrity, SI)分析成为必不可少的步骤。人们知道,在CMOS电路的翻转过程除了受信号上升或下降时间(transition time,也称作slew rate)快慢有关之外,与其栅极的阈值(threshold voltage)极其相关。当输出输入电压的斜率达到1时,即|tan(Vout/Vin)|=1(该点称作统一增益点,Unity Gain Point,UGP),若有临近的并行信号线通过电容耦合(coupling capacitance)产生“噪声(noise)”信号与“受害者”的时钟或者数据信号迭加,就会破坏正常数据信号的传递甚或使得设计失效。

如此可见,标准单元的版图设计结果是产生时序单元格式文件的来源。由于单元延时与信号输入端的翻转时间tslew(transition time)以及负载(CL)相关,因此,时序单元格式文件中的延时函数为f(tslew,CL),用三维表格表示,两个数据之间的中间值使用多项式(polynomial)简化插值方法产生,供计算时序时使用。另一方面,标准单元的功耗信息和信号完整性信息函数同样与(tslew,CL)相关,也用三维表格表示。时序单元文件的时序、功耗和SI等丰富信息,将用于全芯片物理设计过程中的静态时序分析(static timing analysis,STA)、功耗分析和信号完整性分析。芯片代工厂(foundry)通常只提供通用型GP (general purpose) 单元库,例如TSMC从40nm及以下工艺才开始提供低功耗(LP)单元库和超低功耗(ULP)单元库。若采用65nm及以上的工艺,用户应当自行设计,并且产生完整的单元库文件GDSII, LEF 和 “.lib” 等。

在版图设计中人们可以使用工艺设计包(process design kit, PDK),或者称作 “工艺设计锦囊”,这当然给版图设计带来了极大的便利。但是,在很多工程设计中,人们还是离不开很多基础设计步骤。例如,参数化的标准单元(parameterized cell,Pcell)可以帮助工程人员直接定义CMOS晶体管的大小并且直接调用,在28nm或者更先进工艺条件下,还需要考虑制造误差比如光学临近误差(optical proximity correction, OPC)等带来的影响,对版图设计进行校正。

3.集成电路中的半定制版图设计

在半定制版图设计中,例如具有6个晶体管的SRAM或者仅有1个晶体管1个电容的DRAM,它们的标准小单元(RAM cell)高度和宽度尺寸设置与上一节所说的标准逻辑单元无关,需要单独设计,见图4。这一类设计既要兼顾标准版图设计的通用性,又要考虑到重复使用单元在当前模块设计中使用的灵活性。早期英特尔公司的CPU芯片的设计就采用了很多半定制的版图设计,这种版图设计技巧也会用于高性能计算机芯片的CPU设计之中。比如CPU中的数据通道(datapath)部分如果使用标准单元,则往往成为实现高性能的瓶颈,而采用半定制的专门设计,才会更好地提高整个芯片的性能。

图4 半定制版图设计中重复使用的RAM单元具有不同高度与不同宽度

(从左往右: 6T-SRAM单元电路及其版图, 1T1C-DRAM单元电路及其版图)

还有一类特殊的半定制版图称为客户自有技术(Custom-Owned Tooling,COT)模块,在专用集成电路(application specific integrated circuit,ASIC)中经常采用。闪存存取器(flash memory)的基本单元(NAND和NOR单元)与上述SRAM和DRAM的基本单元类似,也是采用半定制版图设计。众所周知,NAND闪存已经广泛用于新型的固态存储器(solid state drive, SSD)中。目前,数字电路基本单元常常工作在几百兆赫兹(MHz)的频率。DRAM新一代产品,即先进的双数据率同步动态存储器(double data rate synchronous dynamic RAM, DDR SDRAM)系列(最新版本为DDR4)和LPDDR系列(最新版本LPDDR5)数据率达到了6.4Gbps),可以广泛用于5G通信和汽车电子的芯片设计中。

上面讨论到,Pcell可以帮助工程人员直接定义CMOS晶体管的大小,可以直接调用或者方便地更换从而对设计不断进行优化。在28nm或者更先进工艺条件下,尤其是模拟电路对工艺参数根据敏感并直接影响到性能。这些问题可以通过约束控制设计(constraint-driven design, CDD)方法加以克服。比如,在进行差分对晶体管设计时,工程人员可以调用约束文件,对差分对电路进行控制配对,实现预定的性能。

与标准时序单元相比,存储器的时序关系比较复杂。通常前者主要关注“时钟(CLK_)”与“数据(DATA_)”信号之间的建立(setup)时间和(hold)时间; 后者还要额外处理“地址(ADD_)”、“控制(CONTR_)”、“读(RE_)” 、“写(WR_)” 、“使能(EN_)”等信号关系。

熟练地掌握了标准单元版图设计之后,对于半定制版图设计方能驾轻就熟,举一反三,并借助CDD方法,很好地处理设计规则并符合工艺制造的要求。一般说来,数字电路的标准单元或者其他电路设计由前端(front-end)工程师完成;版图设计则由后端(back-end)工程师完成。在模拟和混合信号模块或者芯片设计中,电路设计与版图设计溶为一体,才能达到更好的性能要求。

4.集成电路中的全定制版图设计

在模拟和混合信号芯片设计中,更多地采用了全定制版图设计方法;尤其是射频电路的芯片设计,基本上必须通过全定制版图设计来实现,这样才能有效地达到电路的设计目标,比如,信号耦合与匹配,有源区器件和无源区器件的实现,高频参数电感和自感参数的控制和优化等。

模拟和混合信号芯片设计包括常见的模拟前端控制器(analog front-end, AFE)、模数转换器(analog-digital converter, ADC)、数模转换器(digital-analog converter, DAC)、运算放大器(op-amp)和比较器(comparator)等。

5G通信采用的频段规范称作“5G新空口”(5G New Radio,5G NR),使用6 GHz以下频率以及毫米波波段,见图5。数据率为10~20Gbps

图5 5G NR频率和5G NR毫米波频率范围

射频无线通信技术包括蜂鸟(ZigBee,IEEE 802.15.4),无线(WiFi,2.4GHz/5GHz,IEEE 802.11),蓝牙(最新版本Bluetooth 5.0, 2.4~2.483.5GHz)和蓝牙低功耗(Bluetooth Low Energy,BLE, SIG/IEEE 802.15.1)和全球互通微波访问(WiMax, 3.5~5.8GHz, IEEE 802.16d; 2.3,2.5,3.5GHz,IEEE 802.16e)等5种标准。与这些通信技术相关的射频芯片设计包括IoT常用的接口,例如串并联接口(Serial Parallel Interface,SPI)模块,射频功率放大器(RF PA),低噪声放大器(low noise amplifier,LNA),压控振荡器(voltage-controlled oscillator, VCO),混频器(frequency mixer),滤波器(filter)等。

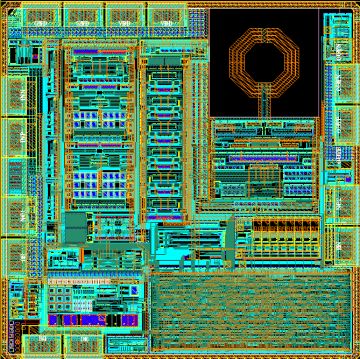

射频无线模块或者独立的射频芯片,从电路设计到版图设计,完全属于全定制设计方式。设计人员在标准版图设计和半定制版图设计的基础上,不断开发出专用的芯片射频产品。图6为某射频公司自行设计的5GHz通信产品全定制版图案例,即版图为全手工设计,芯片制造采用180nm射频工艺,其数据率达到5Gbps。

图6 某射频公司5Gbps通信产品全定制(手工)版图设计案例

蓝牙芯片产品开发相对比较困难,射频的性能与功耗是衡量蓝牙芯片的重要指标,包括数据传输速率、信号延时与稳定性等都是芯片开发与研究的挑战。包括采用40nm的CMOS蓝牙芯片的亚阈值建模与电路仿真,版图后仿真与优化等。目前,不少射频应用芯片已经向40nm以下的先进工艺开发,这时,设计人员需要器件建模(例如BSIM6仿真模型)和全定制版图设计双管齐下。

熟练地掌握了标准单元版图设计和半定制版图设计之后,对于全定制版图设计方能驾轻就熟,运用自如,以CDD方法加以辅助,则更好地处理模拟混合信号和射频设计规则的特殊要求,例如电感和互感对版图的影响,及其工艺制造后的实测结果。

5.高性能与高速芯片设计与版图设计

物联网和5G联网通信中除了信号收发单元(transceiver, TRX 以及TX/RX)设计芯片之外,离不开专用的系统芯片SoC,其中高性能与高速核心IP往往决定了SoC的性能和速度。常见的高性能与高速核心IP有: PCIe, 10 Gigabit Ethernet (10 GbE), RapidIO, SerDes, USB等。表1列出了几种物联网和5G时代常用的高性能与高速IP的信号速度和数据率。

第1代PCIe总线技术最早于2003年提出,它源自英特尔公司的第3代输入输出3GIO技术。2017年PCIe第4代提出,2019年将开发PCIe第5代。英伟达公司注重机器学习中数据处理GPU芯片的开发,目前采用PCIe第2代产品,已经实现了16Gbps数据率。

高速IP接口吉比特以太网10GbE (IEEE 820.3ae-2002)采用全工协议(full-duplex protocol),用来处理以太网的高数据率数据,广泛用于需要高带宽的企业服务器和数据中心等, 表1列出了10GbE (连接MAC层和PHY层的)的两种接口参数,即4通道XAUI模式和单通道XFI/KR模式。

RapidIO用来作为与处理器之间的信号互联,大量用在数据中心和高性能计算机嵌入式芯片设计中,也用于异构系统(heterogeneous system architecture, HSA)芯片中,包括人工智能芯片采用的CPU,DSP,GPU等设计。

表1 物联网和5G常用IP模块的信号速度和数据率比较

由上表可见,使用高速IP时离不开相关IP设计的控制器(Controller)模块和物理层(PHY)模块的设计,它们必须满足3~10GHz信号频率要求,相应的数据率10~40Gbps对于芯片的版图设计充满了技术挑战。

6.当代及未来5G/IoT应用对版图设计技术影响

针对高端数字芯片的性能要求,设计公司为了满足需求,会专门投入研发人员,重新对标准单元库进行电路优化和版图设计,如第2小节中“标准版图设计”所说,还要重新产生一套单元库文件,包括GDSII, LEF和 “.lib”等。对于半定制设计版图,比如COT模块等,除了注意边界处的走线,也要产生“灰盒子”时序文件。IoT相关芯片以MCU为主的SoC, 其中若干种IP模块和无线模块包括NB-IoT, LoRa, 蓝牙等, 给半定制和全定制版图设计带来新的生命。5G时代的应用场景有三种不同的无线接入模式,包括以消费类为主的增强移动宽带(enhanced Mobile Broadband, eMBB)技术,以智慧机器人和无人驾驶等为主的超高可靠超低时延通信(Ultra-reliable low latency communication, URLLC)和大规模机器通信(massive Machine‐Type Communication, mMTC)。这些多样化的应用场景会对射频电路芯片电路与版图设计带来新的技术挑战和产品需求。

因此, 在5G 和IoT时代, 无论是标准单元版图设计,半定制版图设计和全定制版图设计,基本的设计方法得到发扬传承,高性能、低功耗、低成本的要求提得更高,对未来高质量高可靠性版图设计设立了新的规范和起点。例如,用于深度学习的芯片设计,由于涉及到海量数据计算,已经使用算力单位千兆(1012, tera operations per second, TOPS)为参考,使用能效比(TOPS/W)作为衡量芯片架构和设计的总体检测指标。最新的2019年国际固体电路会议(International Solid-State Circuits Conference, ISSCC)分组文章都做了详尽的讨论。

参考文献

[1] 王阳元主编,《集成电路产业全书》,2018年,北京:电子工业出版社(ISBN 978-7-121-34822-8)。

[2] 陈春章,集成电路设计方法中EDA的角色,《微纳创新》,2018年夏,总第08期,第34~39页。

[3] 陈春章,王国雄,艾霞,《数字集成电路物理设计》,2008年,北京:科学出版社(ISBN 978-7-03-022031-8)。

[4] ISSCC 2019,https://submissions.mirasmart.com/ISSCC2019/PDF/ISSCC2019AdvanceProgram.pdf