1.电源处理

如果电源设计时没有经过认真考虑,则使得电源电压很容易产生错误的输出和噪声,这会进一步影响到RF电路的性能,使用不同分支的电源线,为射频芯片的电源引脚供电。每个电源引脚使用独立的引线在引脚之间提供了空间上的隔离,有利于减小它们之间的耦合。另外,每个电源引脚都要做好充分的去藕滤波。

去耦电容存在一定的寄生电感。事实上,电容等效为一个串联的RLC 电路,因此有一个自激振荡频率,电容在低于这个频率时起主导作用,但在大于自激振荡频率时则失去电容的功能而变成了一个电感器件。由此可见,电容器只是在频率接近或低于其自激振荡频率时才具有去耦作用,在这些频点电容表现为低阻抗。理解这些概念有助于我们在PCB设计中去优化处理那些去藕电容的设计。

射频模块对电源噪声比较敏感,所需电流也不大,因此不宜采取平面供电,而是采取走险的方式来供电。这和数字电源系统不同在射频和高速PCB设计中所有的信号地以最短的路径连接到地层非常关键,过孔主要呈现为感性,对于RF电路的接地孔本着永远不共用的原则。一个1.6mm 深、孔径为0.2mm 的过孔具有大约1—3nH 的电感,在2.5GHz/5.0GHz 的频率时其等效电抗大约为12Ω 和24Ω。因此,一个接地过孔并不能够为RF 信号提供真正的接地,对于高品质的电路板设计,应该在RF 电路部分提供尽可能多的接地过孔,特别是对于那些需要有大面积接地的IC ,其封装中的裸露接地焊盘要做好充分接地。不良的接地会出现许多不希望的问题,如产生有害的辐射,降低增益和噪声系数指标。不仅仅是电容应该所有的接地都不共用一个过孔,如果去耦电容使用了同一接地过孔,由于过孔的电感效应,这些连接点的过孔将会承载来自两个电源的全部RF 干扰,不仅丧失了去耦电容的功能,而且还为系统中的级间噪声耦合提供了另外一条通路。

1.1 无LDO、小功率模块

由于模块内未内置LDO,使用者必须严格按照对应的射频芯片的供电要求来处理电源。

一般看情况下我司更推荐将电源波纹控制在20mV(峰峰值)以内,若现场情况复杂不得超过30mV(峰峰值)。

1.2 有LDO、小功率模块

由于模块内已内置LDO,使用者必须严格按照对应的模块的供电要求来处理电源。

一般看情况下我司更推荐将电源波纹控制在20mV(峰峰值)以内,若现场情况复杂不得超过30mV(峰峰值)。

1.3.无LDO、大功率模块

由于模块内未内置LDO,使用者必须严格按照对应的射频芯片的供电要求来处理电源。由于该模块需要较大的发射电流,需要验证供电电路的带载能力。

一般看情况下我司更推荐将电源波纹控制在20mV(峰峰值)以内,若现场情况复杂不得超过30mV(峰峰值)。

1.4.有LDO、大功率模块

由于模块内已内置LDO,使用者必须严格按照对应的模块的供电要求来处理电源。由于该模块需要较大的发射电流,需要验证供电电路的带载能力。

一般看情况下我司更推荐将电源波纹控制在20mV(峰峰值)以内,若现场情况复杂不得超过30mV(峰峰值)。

-2.走线方式

模块应尽量远离电源、变压器、高频走线等电磁干扰较大的部分。

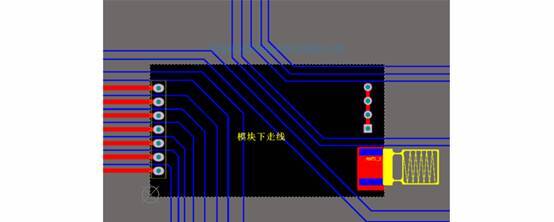

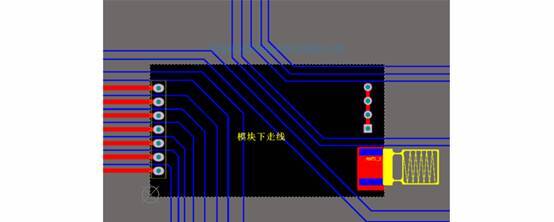

高频数字走线、高频模拟走线、电源走线必须避开模块下方,若实在不得已需要经过模块下方,假设模块焊接在Top Layer,在模块接触部分的Top Layer铺地铜(全部铺铜并良好接地),必须靠近模块数字部分并走线在Bottom Layer。

2.1.典型错误

2.1.1.错误的走线方式一:

如图所示,假设模块焊接或放置在Top Layer,在Bottom Layer或者其他层随意走线也是错误的,会在不同程度影响模块的杂散以及接收灵敏度。

2.1.2.错误的走线方式二:

如图所示,假设模块周围有存在较大电磁干扰的器件也会极大影响模块的性能,跟据干扰的强度建议适当远离模块,若情况允许可以做适当的隔离与屏蔽。

2.1.3.错误的走线方式三:

如图所示,假设模块周围有存在较大电磁干扰的走线(高频数字、高频模拟、电源走线)也会极大影响模块的性能,跟据干扰的强度建议适当远离模块,若情况允许可以做适当的隔离与屏蔽。

2.1.4.错误的走线方式四:

如图所示,含板载天线的模块板载天线周围尽可能不要有走线以及铺铜,这样会极大影响通信效果,并让整机电磁兼容变得很不可靠。

2.2.时钟电路布线

时钟电路要优先考虑,要多琢磨布局的方式,根据实际条件尝试多种方法。优先考虑参考时钟线路的布线,使参考时钟输出到达器件引脚的路线要尽量短,对时钟线尽量采取保护地。同层和相邻层不能有走线与时钟线在位置上近距离平行,在高密度PCB设计时相邻层很容易被人忽略,如果时钟线走在内层最好其上下都为GND,特别要妥善处理好参考时钟线路与功放电源线和射频单元逻辑控制电源线之间的位置。不要选电源平面作为回流参考平面。时钟电路中的寄生电容应该尽量避免和消除,时钟线路接地布线最忌讳的是在未到达主地之前与屏蔽体的地或锁相环的地互连,同时尽量避免孤岛型地的存在,如果可能就优先采取单点直到主地的方法。