1.EVS专利许可乱象凸显,小米等探讨解决方案;

2.吴汉明:国内集成电路面临的问题是对工程文化的忽视;

3.长存创始人杨士宁提出三维异构集成发展三大建议:软硬件共筑生态、持续技术创新、成立自主组织;

4.中科院研究员韩银和:芯粒虽不万能,却是未来几年提升芯片性能的主要技术路径;

5.【一周招/中标】睿励科学仪器新增中标设备3台,尚积新增中标设备2台,上海积塔新增设备招标4台;

1.EVS专利许可乱象凸显,小米等探讨解决方案;

集微网报道 1月12日,由美国知识产权咨询机构Dolcera主办的“EVS技术标准及其费率研讨会”召开。Dolcera CEO Samir Raiyani、小米战略合作部总经理徐然、OPPO知识产权政策总监余媛芳、咨询公司STOUT董事总经理Mitch Rosenfeld围绕EVS专利许可的挑战和展望等问题进行了充分探讨。

锦上添花的技术?蜂窝通信标准的一部分

EVS全称“Enhanced Voice Services”,即增强语音服务编解码器,是第三代合作伙伴计划(3GPP)面向4G/LTE应用制定的标准之一。据Samir Raiyani介绍,EVS的主要应用场景是听音乐和语音通话。EVS的前一代技术是AMR-WB(Adaptive Multi-Rate Wideband, 自适应多速率宽带编码)。AMR-WB技术大幅度提高了3G网络的通话质量。EVS与其前代技术AMR-WB相比,在数据传输效率、带宽覆盖范围等方面均有显著提升。不过,EVS的一个重要提升是其改善了通话期间的音乐质量,该技术应用场景目前看来相当局限。

因为应用场景的局限性,大多数人甚至没有听说过这项技术。基于同样的原因,这项技术的价值也难以一概而论。正如徐然所说:“EVS的价值取决于产业角度,对于网络运营商来说,出于提升效率、充分利用带宽的考虑,可能会希望在其网络功能中采用这项技术;对于芯片组制造商来说,从充分利用EVS功能来为自己的产品增加价值角度,也会支持EVS技术;而对于终端设备制造商来说,往往没有太多选择,因为需要从芯片供应商处获得芯片供应,并从网络运营商处获得入网许可。但从用户体验角度来说,这项技术能给终端设备制造商带来多少价值呢?目前很少有用户能在通话中区分EVS和其前代技术。”

余媛芳从终端制造商角度补充说:“现在的智能手机具有非常丰富的功能,这些功能由大量专利技术支持,包括2/3/4/5G、WiFi、蓝牙、视频编码器、音频编码器、快速充电等。根据3GPP的定义,EVS只是3/4/5G技术的一小部分,且不是核心。主要用于部署在LTE和5G语音上,以提升语音通话性能,然而据我所知,EVS还没有广泛应用于LTE和5G语音上。因此,现在我们很难看到巨大的价值,这可能更像是一种锦上添花的技术。”

EVS许可现状:超出5G费率十多倍

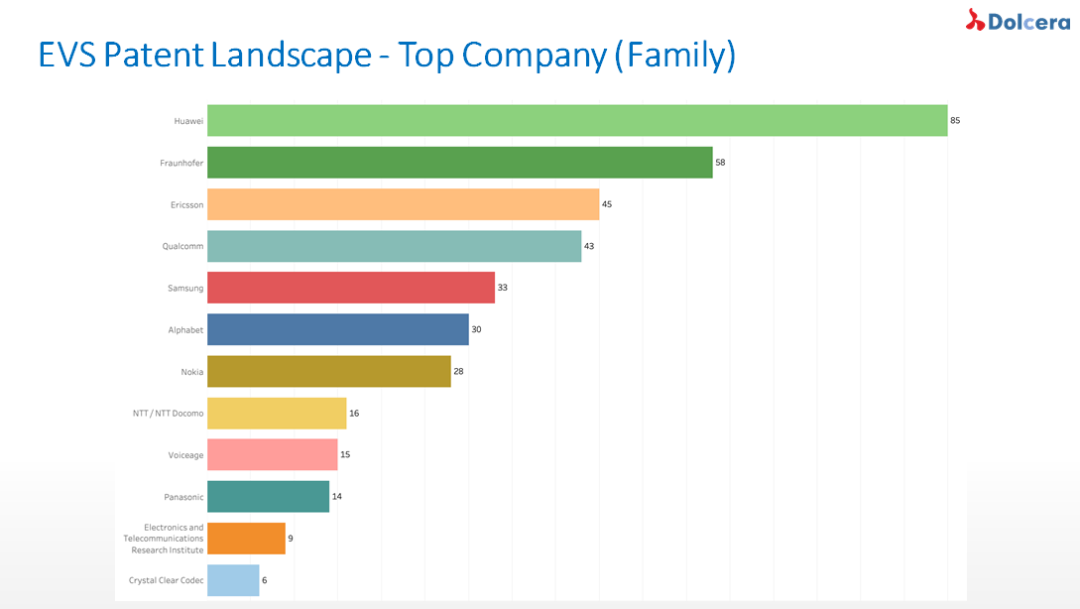

图示:EVS专利权人排行

据STOUT发布的《EVS专利概览》(Enhavced Voice Services, Patent Landscape),截至2022年,EVS标准下声明的标准必要专利(SEP)共计350族,其中有效族数为339族,约占3GPP 3G-5G SEP总量的0.61%。按照行业惯例,EVS专利许可费率也应与这一份额相匹配。然而,据STOUT的测算,目前公开的EVS费率比5G费率还高十倍乃至百倍。

以TCL诉爱立信案和Unwired Planet诉华为案两个成型判例为依据,4G许可总成本应占手机总成本的6%至10%。相应的,EVS的许可成本应占手机总成本的0.036%到0.061%。以410美元的手机平均售价计算,EVS许可成本应为0.15美元-0.25美元左右,平均到每族专利,其价值应在0.0004美元-0.0007美元之间。

图示:EVS许可人及费率概况

目前公开宣布EVS许可费率的有三家机构:VoiceAge EVS、Crystal Clear Codec、MPEG LA,各自公开费率如上图所示。换算为单族专利价值,收费最高的Crystal Clear Codec公布的EVS费率比其应有价值高出足足百倍。

图示:部分专利权人5G SEP费率

事实上,即使将上述EVS费率与主要专利权人公布的5G费率相比,也有数十倍乃至上百倍的溢价。如果按照Crystal Clear Codec的收费标准,EVS技术的总许可成本将堆叠至15美元/设备,蜂窝通信专利许可成本更将达到2459美元的天价。这显然不是终端设备制造商所能承担的合理费率。

许可困境:部分EVS运营NPE不经谈判直接诉讼

令EVS许可的行业环境更不健康的是,EVS的专利权人对使用诉讼的偏好。公开信息显示,自EVS标准化以来,相关技术的运营NPE(Non-Practicing Entity, 非实施实体)已经把所有手机企业告了个遍,包括苹果、HTC、摩托罗拉、小米、LG电子、索尼等。余媛芳提及,有部分EVS运营NPE甚至不首先谈判就直接进行诉讼。HMD近日也在其官网上宣布,该公司已经向欧盟委员会提交了针对VoiceAge EVS的投诉。

对于这一系列EVS许可的乱象,徐然认为,专利池可能是一个好选择,“例如MPEG LA的一个音视频专利池 – AVC(Advanced Video Codec, 高级视频编码)专利池就是行业中一个非常好的例子。AVC专利池汇集了大部分的AVC专利,形成了单一的平台,提供一站式许可方案,几乎每个相关被许可人都从这个池子里得到了许可。当然这将是非常具有挑战性的工作,因为一些NPE已经开始了许可工作,他们的要价很高,把大家重新汇聚到一个市场接受的专利池来许可是不容易的。但是,我认为这还不太晚,我仍然希望看到这种努力被业界采纳,并在未来能够被市场接受。”集微网了解到,MPEG LA AVC专利池通过制定合理费率,汇集大部分AVC专利,提供一站式许可,不仅获得几乎所有被许可人的认可,避免了许可活动中的纠纷,被许可人获得专利许可的同时权利人也获得了合理的回报,而且极大推广了AVC技术,丰富了市场上包含AVC技术的设备,让最终消费者真正地享受到科技带来的美好生活。

Mitch Rosenfeld也认为专利池可能是应对EVS许可问题的答案。他提到,Via Licensing专利池正在探讨建立EVS专利池的可能性。“这样的EVS专利池是否对所有人来说有更大的吸引力,我们将拭目以待。”

值得一提的是,尽管前路尚不明朗,与会嘉宾,不论是许可方还是被许可方,均表达了共同协商直面挑战的意愿。“希望最终我们一起探寻出一个解决方案,既可以适当地补偿专利权人的研发投资,同时也允许实施者以合理的价格出售消费者可以负担得起的手机设备。”这对于EVS许可的前景显然是个好消息。

2.吴汉明:国内集成电路面临的问题是对工程文化的忽视;

集微网消息,1月15日,清华大学集成电路学院集成电路高精尖创新中心主办的第七届未来芯片论坛上,中国工程院院士、浙江大学微纳电子学院院长吴汉明教授指出,集成电路产业以工科为主,由科学催生工程文化发展,现阶段国内亟待加强工程文化的建设,后摩尔时代为卓越工程师成长提供了绝好机遇。

吴汉明表示,随着工艺进步越来越无法支撑算力增长的需求,后摩尔时代半导体技术演进朝着四个方向发展,主流技术挑战均面临着更高的晶体管密度及更多架构、更多的存储类型、更紧密的系统集成(Chiplet微纳尺度集成封装)、先进的EDA工具(提供点到点的优化)等。

事实上,当前国内高校有很多半导体前沿领域的研究成果,但是真正实现产业化的非常少。吴汉明认为芯片制造技术成果转化的特点主要有两个,一是转让,是将技术成熟、可以在生产上直接应用的成果,在其使用范围内加以应用和推广,扩大生产规模;二是转化,将实验室去的的初试成果进行研究开发和中间试验,使之成为生产上可以直接采用的成熟技术,实现大生产。“在后摩尔时代碎片化的市场下,芯片制造成果转化的核心是演示生产可行性,也就是中试环节验证。可以说,缺少中试的技术转化难以生产化。”他强调。

为此,浙江大学在2021年7月建成了一条55纳米中试平台,并已实现了55纳米SRAM的AA、Poly/CT、铜互连多项技术以及器件性能对标国内先进工艺水平,在晶圆级Chiplet方面也可以提供成套工艺技术支持。

随着Chiplet成为大势所趋,吴汉明指出在该领域面临诸多技术挑战,包括基于55纳米的嵌入式硅桥(EMIB)设计、制造与芯粒组装;基于55纳米的有源硅转接板的设计、制造与芯片组装;面向Chiplet、大芯片设计的EDA点工具;晶圆级芯粒系统(大芯片设计):类脑芯片、存算一体芯片、依辛计算芯片、DPU芯片等等。在上述方面浙江大学团队计划与封装企业、清华大学等展开合作。

“中试平台的使命是卓越工程师的培养、推动成果转化。”吴汉明强调,“构建以集成电路产业链为核心的创新网络,提供科研成果的产业会验证平台,打通产业链与创新链。”

“我们的集成电路面临的问题,是对工程文化的忽视。”他指出。针对科学导向偏重的问题,吴汉明举例道,从原始创新的角度讲,中国在1958年就研究出了第一块硅单晶,比美国晚6年,比日本早2年。当时国家虽然穷,但该项科研突破仍然排在世界前列。随着以产能增加为标志的产业发展,中国与其他国家的距离逐渐被拉开,这就是一个典型的仅仅依靠科学导向、忽视工程科学的结果。“我们国家在半导体领域的起步并不晚,但是差距拉开一个关键原因是忽视工程文化的建设。芯片制造不是科学原理需要突破的问题,科学原创问题少之又少,而是体系化、系统性工程技术突破的问题。”

芯片制造是工程,也是艺术,在制造过程中要求全方位的卓越,工艺几乎达到人类生产技术的极限。集成电路产业链的复杂性,要求人才培养需从学科分布到专业设计进行科学、系统规划。

为此,吴汉明呼吁,尽快建设科教协调、产教融合、以人才培养为核心的集成电路制造领域协同创新公共平台,避免工科理科化。加强工程教育、加强技术成果转化和培养大批卓越工程师和实践经验的技术人员,在真实的实践中能够造就工程师独特的工程哲理和专业精神。(校对/赵月)

3.长存创始人杨士宁提出三维异构集成发展三大建议:软硬件共筑生态、持续技术创新、成立自主组织;

集微网消息,1月15日,在清华大学集成电路学院集成电路高精尖创新中心主办的第七届未来芯片论坛上,长江存储、芯盟科技创始人杨士宁在第七届未来芯片论坛上发表了以《芯粒技术:引领芯片步入未来》为主题的演讲稿。

杨士宁指出,大数据、物联网、云计算、元宇宙等应用对数据和计算能力需求极大,整个应用端对集成电路的集成度、性能的提高速度没有丝毫减弱的迹象。然而摩尔定律已经趋缓,业内都在思考使得芯片性能跟上应用端需求的解决方案。

“从1965年到2015这50年间是摩尔定律的辉煌时期,但到2015年,即40纳米到28纳米工艺节点时,摩尔定律发展速度变缓。2015到2025年将是一个过渡期,需要大量的结构、材料创新来勉强支撑摩尔定律的发展。到了2025年以后,高性能芯片对集成度、性能的要求极高,三维异构集成将必然发展趋势。”他解释说道。

杨士宁表示,“芯粒现在很火热,并不是说它是一个新事物,实际上是三维异构集成有了新能力。整个行业本来就是从小芯片开始,只是我们推进到SoC做大芯片了,现在走不下去了,又要退回去把Soc拆开。最终我们要推动的方向是要有能力把多颗小芯片集合成一颗单芯片,因为单芯片才有很快的通道、很低的运算数据传输,芯片和芯片之间可以直接互联,而且互联的节奏是在百万级以上。”

据他介绍,三维异构集成的应用非常广泛,包括高性能计算、自动驾驶、元宇宙等。“它不仅是存算一体化,实际上还是逻辑和逻辑,如果逻辑芯片之间的工艺、成本差别很大,最后可以用维异构集成把它对接成同一个工艺。”

杨士宁同时指出,三维异构集成应用仍需跨越六大门槛。一是需要多平台的设计和工艺的专家;二是集成工艺突破;三是三维异构设计IP,特别是要解决数据怎么对接,存储器怎么控制的问题;四是接口的标准化;五是产品的整体架构的拆解和重组;六是不同阶段测试如何到位。

基于此,行业急需一个能力完整且中立的异构集成支持平台。芯盟科技三维异构集成已有4年发展历程,能够提供三维异构集成设计+制造全周期一整套服务,包括IP开发和授权、基于HITOC技术的集成设计以及后续方案等。

最后杨士宁提出了对异构集成发展的几点建议。一是实际上异构集成是需要设计、软件、硬件、制造协同合作的一个生态,所以行业内的互相交流非常重要;二是这个领域比较新,需要不断进行技术创新、不断投入;三是要成立类似“UCle”的自主组织,协调业内在硬件、设计的创新以及架构的重组。(校对/王云朗)

4.中科院研究员韩银和:芯粒虽不万能,却是未来几年提升芯片性能的主要技术路径;

集微网消息,1月15日,在清华大学集成电路学院集成电路高精尖创新中心主办的第七届未来芯片论坛上,中科院计算技术研究所研究员韩银和表示,芯粒虽不是万能的,却是未来几年提升芯片性能的主要技术路径,这条技术路径对我国更有利。

韩银和指出,高性能芯片是国家战略产品、数字经济基础,也是受制于人的重灾区,我国芯片自给率极低,集成电路是我国第一大进口商品。高性能芯片也是整个电子信息产业的核心和基础,整个产业对算力需求持续增长。

“然而算力危机也随着神经网络的迅速发展而出现,即应用算力的超摩尔定律需求和芯片摩尔定律增长迟缓之间的矛盾。为了破解这一危机,业内开始探索新的技术路径。”他说道。

业内周知,增加芯片面积是提高算力的重要手段之一,但这种方法会遇到面积墙问题,目前光刻机口径、成本、良率等限制使得单die面积无法持续增加。

为了突破面积墙问题,业内提出了大芯片概念,“所谓大芯片,就是面积大于一个光罩制造尺寸,同时采用半导体制造技术来集成的芯片。”韩银和解释说道。

目前做大芯片有两条技术路线,一是晶圆级平面大芯片,二是用芯粒集成大芯片。韩银和表示,在平面上做大芯片会面临良率、供电、散热、热应力等各类挑战。我们主要的技术路径是后者,优势在于三维集成能够大幅提高晶体管总量,同时芯粒的模块化能够降低芯片设计时间和成本。

“芯粒技术已成为高性能处理器的重要使能技术,正朝3D集成、更大规模、更大数量、更多种类趋势发展。”韩银和补充说道。

接下来,韩银和指出芯粒集成大芯片正面临四个需要解决的科学问题。一是如何设计并行架构和机制,以提升并行计算效率;二是如何设计访存结构和互连,以提升访存能力;三是如何设计高性能和新结构基板,以支撑规模扩展性;四是如何设计散热、供电、应力结构和机制,保证可靠性。

针对上述问题,中科院计算技术研究所和之江实验室正在开展之江大芯片项目,于2020年开始相关工作,目标探索大规模芯粒集成大芯片的体系结构、编程方法、散热结构等关键使能技术,以研发出万核处理器。

最后,韩银和指出,芯粒虽不是万能的,却是未来几年提升芯片性能的主要技术路径。这条技术路径对我们更有利,它是半导体硅工艺的延续,涉及到设计、EDA、制造、封装全流程,应用需求牵引芯片和封装等在其中扮演越来越重要角色,而这是我国相对具有基础的领域。(校对/王云朗)

5.【一周招/中标】睿励科学仪器新增中标设备3台,尚积新增中标设备2台,上海积塔新增设备招标4台;

集微网消息,本周,新昇半导体新增设备招标9台,上海积塔新增设备招标4台,西安奕斯伟新增设备招标1台;睿励科学仪器新增中标设备3台,尚积半导体新增中标设备2台,逸典科技新增中标设备2台,ASE新增中标设备6台,东京精密新增中标设备3台,Optima新增中标设备2台。

重要招标数据:

本周招标16台设备,其中,薄膜沉积1台,工艺检测2台,CMP 6台,清洗设备1台,涂胶显影1台,其他设备5台。

重要中标数据:

本周中标98台设备,其中,刻蚀设备1台,薄膜沉积7台,工艺检测8台、CMP 12台、清洗设备7台,其他设备63台。

本周重点企业动态:

近日,杭州富芯12英寸模拟集成电路芯片生产线项目(一期)具备竣工规划确认条件;北方华创在投资者互动平台表示,公司多种新设备已实现在28纳米产线的应用;盛美上海在接受机构调研时表示,今年会推出多种膜的PECVD,在客户端进行验证;华海清科在接受机构调研时表示,公司减薄产品预计2023年会有小批量出货,湿法设备已应用于公司晶圆再生生产;芯源微临港研发及产业化项目主体结构封顶;北京烁科中科信发布消息称,开年新签整机累计达11台,合同总额突破2亿元。

以下是本周部分招标信息汇总:

以下是本周部分中标信息汇总:

(校对/韩秀荣)