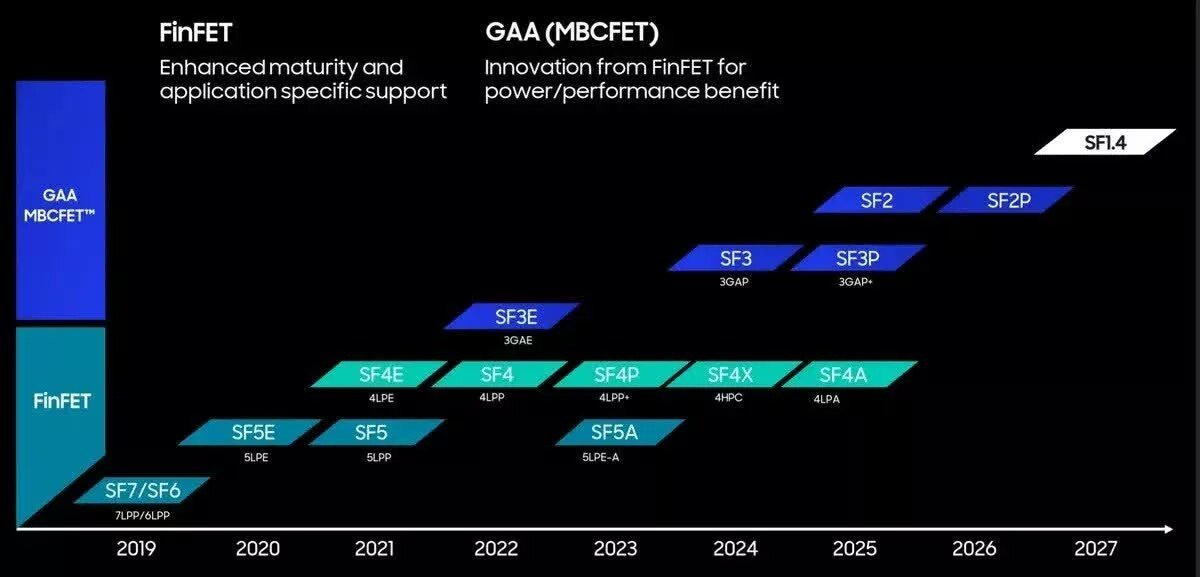

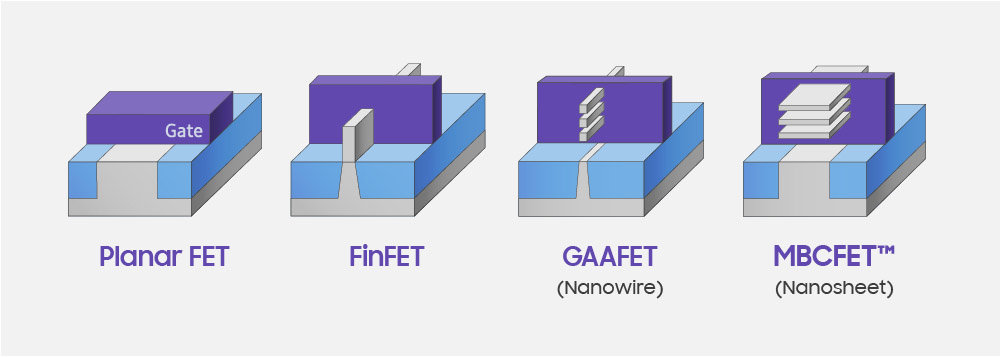

三星在去年6月量产了SF3E(3nm GAA),这也是三星首次实现GAA“多桥-通道场效应晶体管(MBCFET)”应用,打破了FinFET原有的性能限制,引入全新的GAA(Gate-All-Around)架构晶体管技术,通过降低工作电压水平来提高能耗比,同时还通过增加驱动电流增强芯片性能。

2023年VLSI技术和电路研讨会将于2023年6月11至16日在日本京都举行,根据官方的预告,三星将介绍名为SF3(3GAP)的第二代3nm工艺技术,将使用“第二代多桥-通道场效应晶体管(MBCFET)”,在原有的SF3E基础上做进一步的优化。

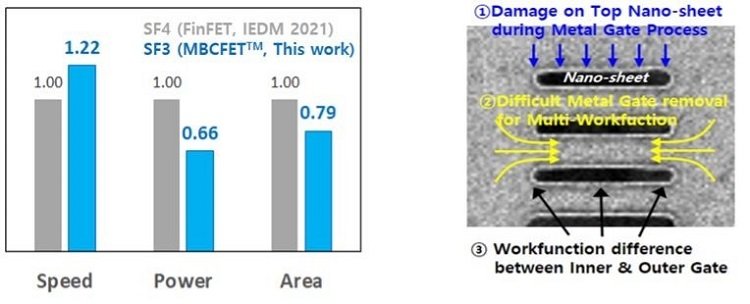

三星表示,与SF4(4LPP,4nm级低功耗工艺)相比,SF3在相同功率和晶体管数量下的性能提高了22%,在相同频率和复杂性下的功耗降低了34%,逻辑面积缩小了21%。不过三星并没有将其SF3与SF3E进行比较,也没有关于SRAM和模拟电路缩放方面的资料。

与FinFET相比,GAA的主要优点之一是泄漏电流减少,另外通道厚度可以调整,以提高性能或降低功耗。三星表示,新的SF3提供了更大的设计灵活性,使用不同宽度的MBCFET器件。暂时不清楚现有的SF3E是否缺乏GAA架构晶体管最关键的技术之一,但三星的介绍似乎暗示了这一点。

凭借SF3,三星有机会在2024年与台积电(TSMC)的先进工艺展开竞争。最近三星承认其半导体制造工艺上落后于台积电,不过认为更早地采用GAA架构晶体管技术是一项优势,希望五年内可以实现超越。

三星还在改进其4nm工艺,目标是通过SF4P(4LPP+)缩小与竞争对手之间的差距,预计会在今年晚些时候量产。此外,三星还计划推出用于高性能CPU和GPU的SF4X(4HPC),不过在几乎同一时间,台积电也会带来名为N3P的增强型3nm工艺。