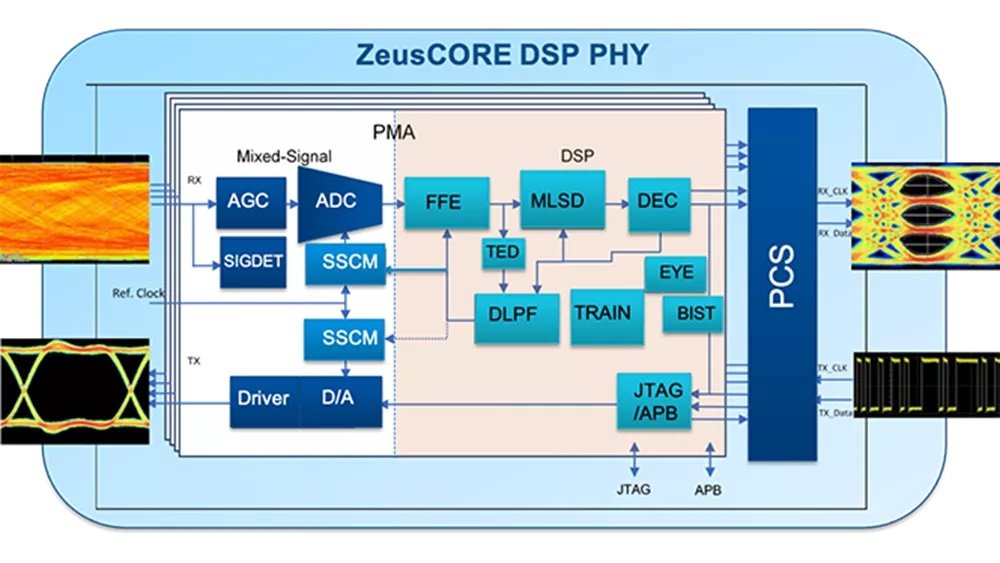

近日Alphawave宣布,推出ZeusCORE100 1-112Gbps NRZ / PAM4 串行/解串器,支持800G以太网、OIF 112G-CEI、PCIe 6.0和CXL3.0在内的众多标准,这也是其采用N3E制程的首个测试芯片。目前该芯片已通过所有必要的测试,稍后会在台积电的OIP论坛上展示。

Alphawave首席执行官Tony Pialis表示,很自豪成为首批使用台积电最先进3nm工艺技术的公司之一,双方的合作伙伴关系将继续带来创新的高速连接技术,为最先进的数据中心提供动力。

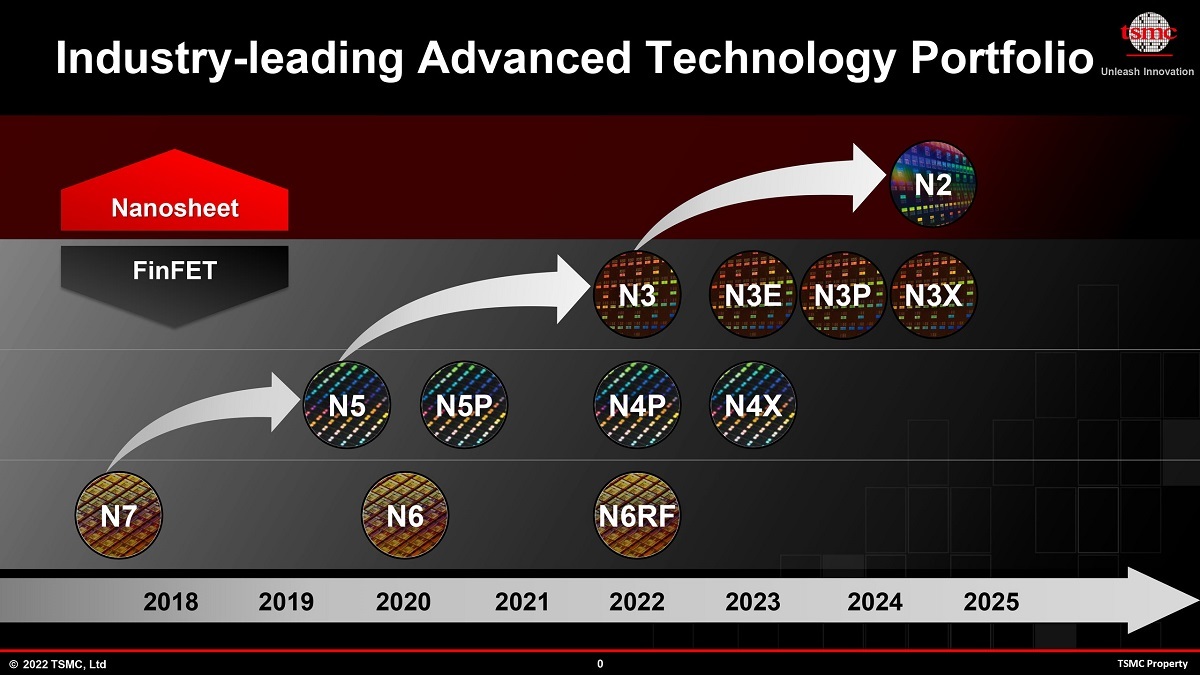

如果将N3和N5制程做比较,前者预计会带来10%到15%的性能提升(相同功耗和复杂程度),或者降低25%-30%的功耗(相同频率和晶体管数量),同时会将逻辑密度提高约1.6倍。N3E是台积电(TSMC)第二代3nm工艺,相比N5制程,性能提升幅度大概为18%,或者降低34%的功耗,逻辑密度提高约1.7倍。相比N3,预计N3E会更广泛地被采用,量产时间为2023年中旬或第三季度。

台积电从2022年到2025年,将陆续推出N3、N3E、N3P、N3X等制程,后续还会有优化后的N3S制程,可涵盖智能手机、物联网、车用芯片、HPC等不同平台的使用需求。台积电在N3制程节点仍使用FinFET(鳍式场效应晶体管),不过可以使用FINFLEX技术,扩展了工艺的性能、功率和密度范围,允许芯片设计人员使用相同的设计工具集为同一芯片上的每个关键功能块选择最佳选项,进一步提升PPA(功率、性能、面积)。