最近有业内消息称,台积电将会在下个月开启5nm制程的大规模量产,上周六,WikiChip将他们从各种会议上掌握到的台积电5nm工艺信息整理成了文章,本文就简单介绍一下台积电5nm制程的一些特性与它达成的目标。

图片来自于WikiChip,下同

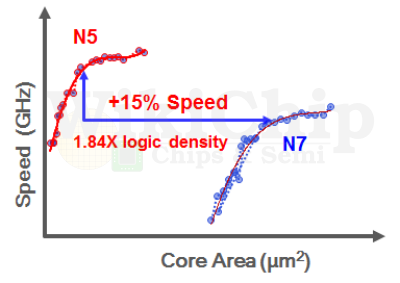

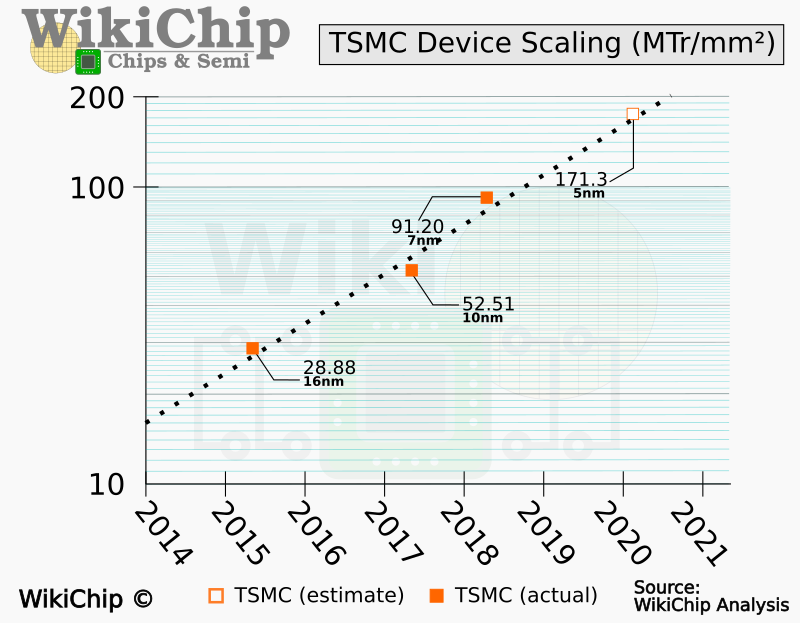

WikiChip预测台积电的5nm工艺密度将达到171.3MTr/mm2,而在IEDM上面,台积电公开密度提升有1.84倍,与WikiChip预测的1.87倍十分相近。

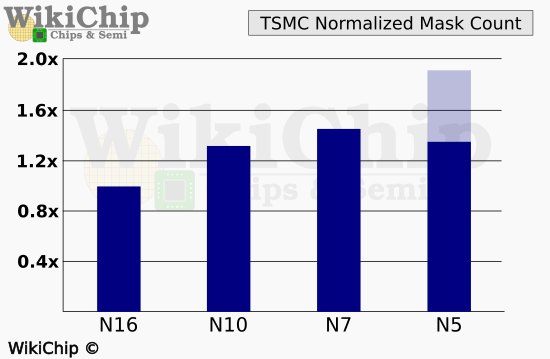

台积电N5工艺使用的EUV掩膜

根据台积电在IEDM会议上面的发表,WikiChip推测它的栅级间距为48nm,最小鳍片间距为30nm,相对于N7工艺,前者是0.84x,后者则是0.75x。单元高度仍为6T,与N7工艺相同,另外N5 HPC可能将会把单元高度扩大到7.5T。

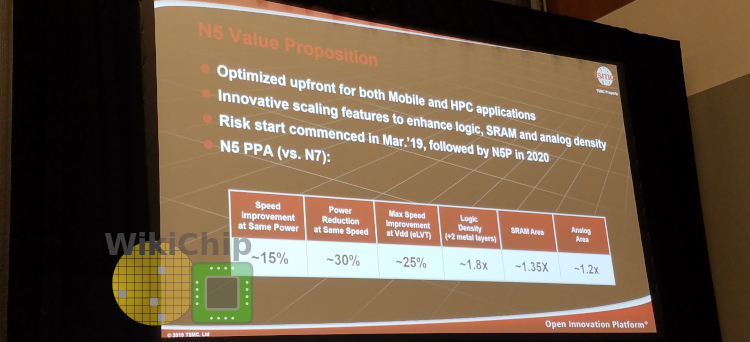

然后看到工艺在性能和功耗上面的改进,在IEDM上面,台积电介绍N5在同能耗下能够提升15%的频率,在同频率下降低30%的能耗。另外,对于由60%逻辑电路、30%SRAM和10%I/O电路组成的典型移动SoC,N5能够让它的尺寸减小35%~40%。

N5除了N7时代就有的uLVT(ultra-LVT)工艺外,还新增了一种eLVT(extreme-LVT)工艺,相比起N7 uLVT,它能够提升25%的频率,而在不追求极限密度的N5 HPC工艺下,它相比uLVT还能提高10%的频率。

台积电强调N5将会大规模使用EUV光刻,而实际上这将会是台积电的首个主要EUV节点。因为N7+不兼容原有的电路设计,基本上没几个客户用,而台积电也将N5设计为N7主要的迁移节点。

通过大规模引入EUV光刻,台积电成功地减少了N5所需的掩膜数量,上图是将N16所需的约60层掩膜作为底数算出来的情况,如果N5没有使用EUV光刻,那么它所需的掩膜数量将从N7的1.45x激增到1.91x。而在EUV光刻的帮助下,N5使用的掩膜数量甚至比N7的87层还要少,约为1.35x/81张。台积电使用了约10层EUV掩膜,它们成功取代了至少4倍的DUV层。

另外,台积电还在N5上面引入了高迁移率通道(High-mobility Channel)这项新技术来改善驱动电流的情况。官方并没有给出具体实现情况,不过WikiChip认为台积电可能为pMOS期间使用了SiGe通道,也就是引入锗元素。它将会带来约18%的性能提升,相当可观。

N5的其他改进还有Scaling Boosters和内部互联,不同都没有公布太多细节。

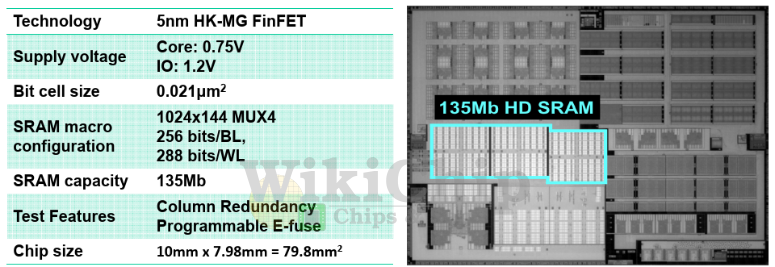

N5对于SRAM生产有两种库,高密度(High-Density)和高性能(High-Performance)库,前者的单元面积为0.025μm2,后者的面积为0.021μm2,无论采用哪种库,其密度都是迄今为止最高的。

在N5制程下,用作L1缓存的SRAM可以在0.85V电压下跑到4.1GHz,如果将电压提高到0.9V,其频率还可以进一步提升到4.2GHz。

台积电测试芯片的规格

在年内我们应该能看到应用台积电N5工艺的SoC,比如说苹果的A14和华为的下一代旗舰SoC。要上桌面端的话,还是要等等,高密度带来的一个问题就是高积热,这是很难解决的。

如果台积电的N7还不能说是完全领先于其他家的话,那么N5是真的拉开了很大的差距,三星的N5密度比台积电的低太多了,而Intel的7nm也许可以追上,但是还要很长的时间。