又是一个午夜,错误究竟出在哪?

兰州大学信息科学与工程学院2019级本科生陆钇桦一遍遍检查调试代码,一筹莫展时向“战友”求助。不到一分钟,同为2019本科生的团队负责人梁泽成打来了电话。“谢谢,早点休息。”挂断电话,陆钇桦长舒一口气,时间已是凌晨三点。

一年来,这样的场景不知上演了多少次,每个人都焦虑过,但团队7名本科生凝成一股绳,付出终有回报。近日,由兰州大学信息科学与工程学院“一生一芯一系统”本科生团队自主研发设计的同、异步混合架构的面向嵌入式的RISC-V处理器已经成功完成流片和回片,经初步测试,该芯片功能正常,完全达到设计的预期目标,可用于控制智能家电、医疗设备、汽车工业以及IoT控制器等场景。目前,该项目已在gitee网站上开源,供全世界的芯片设计爱好者参考。

代码要敲,芯片也要做

每个周四、周五下午,在兰州大学城关校区飞云楼何安平副教授的实验室,70平米的空间内,20多位“一生一芯一系统”项目第二期成员从榆中校区赶来,自发组成几个研讨小组,争得面红耳赤只为了对芯片的系统架构设计问题做最终的梳理和确认。每到周末,他们还会在线上共同探讨项目进度,规划分配好下一步工作。

第2期成员在实验室进行小组研讨

时间回溯到2020年,何安平在与其他高校的交流中了解到,有些头部高校正尝试带领本科生做一些CPU芯片研发工作。同一课程组的周睿副教授也认为,当前对计算机类人才的培养强调计算机系统能力,这一概念体现了对计算机软硬件综合设计与开发的要求,因此既要培养同学们的软件开发能力,也要加强同学们对硬件的认识和理解。

“随着我国芯片行业的发展变化,学院意识到无论是学习计算机软件还是硬件的学生,都应该知道如何研发CPU,架通软硬件之间的桥梁,加强本科生计算机系统能力的培养。”学院党委书记陈文波说。

2021年6月,由信息科学与工程学院的《计算机组成原理》、《嵌入式系统原理及开发》和《数字逻辑》课程组联合启动了“一生一芯一系统”研发项目,经过同学们自主报名,第一期芯片研发项目共吸纳了计算机类专业、电子信息类专业,以及物理学院微电子专业的7名本科生。

对于没有任何CPU芯片开发经验的本科生来说,确定研发目标是个大难题。“一方面我们考虑了学生的实际情况,另一方面我们也希望目标制定得相对高一点,让学生踮起脚跟,伸开手臂才能够得着。”何安平说。

本科生大二会学习《数字逻辑》、《计算机组成原理》等基础课,初步具备开发CPU的理论知识。另外,何安平团队经过多年探索,在芯片研发领域积累了较为丰富的经验,去年成功流片首颗极大规模全异步电路芯片,成为同学们的“定海神针”。

过程很难,实现之后就是了不起的事情

在一个6毫米的正方形包装里,内嵌着一个总面积为4.4平方毫米的小芯片。经过长达半年的等待,2022年12月,一百多颗成功流片的嵌入式芯片终于来到了兰州大学,命名为兰大RISCV处理器(LZU RISC-V Processor,livp)1号。

部分成功流片的芯片

经过师生广泛阅读国内外优秀论文案例、反复讨论,团队决定做一款嵌入式CPU。目前,嵌入式CPU是行业内使用最广泛的中央处理器,全球每年的出货量可达几十甚至上百亿颗。它设计起来相对简单,通常被用于控制和执行设备的特定功能,如监控传感器数据、控制电机、图像处理、网络连接,在教育医疗、智能家居、数控机床、汽车等众多领域发挥着不可替代的作用。

嵌入式系统的开发离不开指令集架构,且嵌入式CPU通常基于ARM或MIPS等指令集架构设计,但是团队最终选择了RISC-V指令集。

目前大部分指令集架构,要么需要昂贵的授权费,要么不适用于嵌入式系统开发。而RISC-V具有低功耗、低成本、全面开源等特性,其开源的特性允许任何用户自由修改及扩展,大大降低了定制指令集修改的门槛。随着物联网时代来临,嵌入式终端设备对功耗和性能具有更高的要求,RISC-V作为新兴指令集架构以其精简的体量,表现出了较强的优势。

“一开始我们对于这个指令集了解很少,为了弄清楚处理器架构的问题,我们几个人在秦岭堂B201的黑板上画来画去。一路走来,真的经历了很多困难。”2019级电子信息科学技术专业的魏人说。

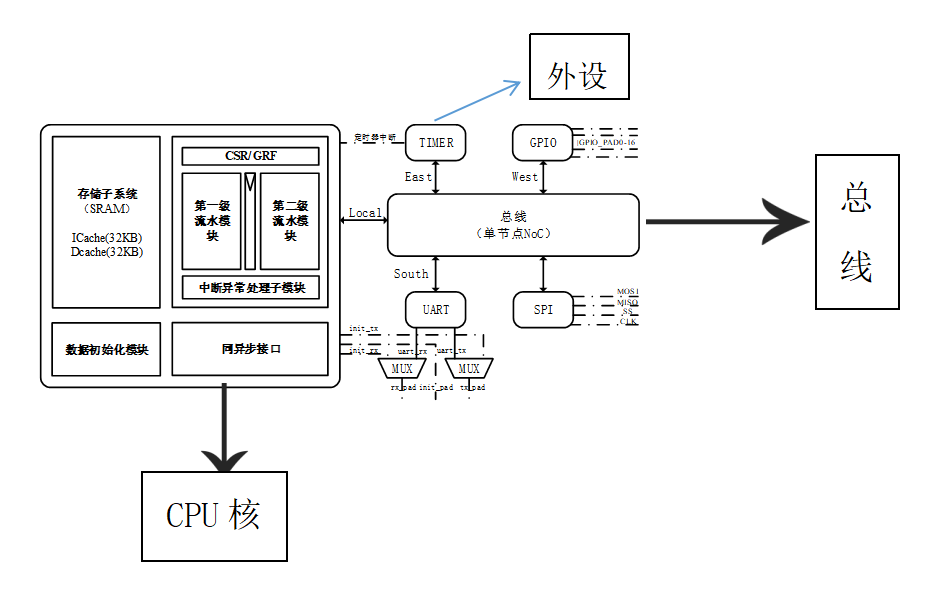

指令集架构是CPU设计的核心,如同人类的语言系统一般,CPU各个模块之间相互理解依赖于共同的指令集。CPU核、总线和外设三部分组合,构成了片上系统这一整体。

CPU核是整个运算处理单元的核心,采用的是两级流水单发射架构,主要包括第一级流水模块,第二级流水模块和中断异常模块三部分。

“这种两级流水架构相当于工厂中的流水线,每条指令都可以分为第一级流水和第二级流水两个阶段,且两级流水的电路能够同时执行不同的指令,有效提高了运算效率和电路的利用率。而中断异常处理模块可以对访问存储器异常等异常情况和中断请求进行处理,根据原因执行相应的程序。”陆钇桦介绍。

总线上挂载了4个外设,如UART接口、TIMER定时器等,这些外部设备可以与外界进行通信,数据可以通过总线在CPU核和外设之间进行传输。

芯片系统架构图展示

livp芯片系统整体架构设计阶段结束后,团队成员迅速进入到编码阶段。为了提高效率,团队进行小组分工,每个小组负责一个模块,各个小组成员充分利用周末及其他课余时间,定期进行模块与模块之间的沟通与协商,遇到问题及时调整方向。“有时候讨论累了我们就出去团建吃顿饭,或者一起去爬学校后面的萃英山,回来之后继续交流讨论项目细节。”已经上研的团队成员、2018级本科生张灵壮笑着说。

尽管编码调试阶段遇到了很多困难,但是团队中队员们互相帮助、互相加油打气,总是以“过程很难,实现之后就是了不起的事情”来鼓励彼此。“在临近芯片交给代工厂进行流片的前一段时间,大家为了保证芯片设计的质量,不断进行验证测试。白天做不完就熬夜做,团队里很多人自愿留在实验室通宵。当时什么也顾不得,只想着一定要做到最好,不能让之前的努力付诸东流。”2019级本科生李勋说。

这群本科生团队从0开始,经过1年的时间,一步一步完成了芯片架构制定、芯片代码设计、FPGA验证和ASIC实现等一系列芯片设计的全流程工作。2022年7月,采用联电110nm制程工艺的livp芯片顺利送往代工厂进行流片。

2022年12月,livp芯片成功回片。“当何老师告诉我们芯片流片已经到实验室的时候,还是感到有些不可思议。”陆钇桦小心翼翼地接过一颗芯片放在手心,感觉过去一年的经历都是值得的,高兴、自豪、激动的情绪掺杂在心头。

livp芯片最大的突破在于采用了同异步混合电路,CPU核运用同步电路设计,使用统一的时钟驱动,这也是目前较为主流的设计方式。而总线采用的是全异步电路,设计起来比同步电路更加复杂,但具有低功耗、高功效的特点。

让所有学生都参与进来

安装上芯片的电路板

今年年初,《嵌入式系统原理及开发》课程组负责人王兆滨副教授带领同学对芯片各项功能进行了测试。为了方便测试,师生做了一个5cm×3.5cm的电路板。“单颗芯片是没有办法工作的,我们需要把芯片和外围电源、时钟等电路连接起来,这个电路板实际上就是维持芯片正常工作的一个最小系统。”连上电源,输入相关指令,便可使用相关仪器对芯片的输入输出信号进行检测。经过初步测试,该芯片的各项功能正常。

对芯片进行性能测试

下一步,周睿打算带领学生移植或定制一个适用于上述硬件的小型操作系统,能够让它运行一些既简单又能体现一定特色的应用程序,从而实现一个较为完整的计算机原型系统。

一颗小小的芯片嵌入到电路板上,操作系统也即将被构建,“一生一芯一系统”项目的第一期工作也接近尾声,而兰州大学信息科学与工程学院对计算机人才的创新型培养却在加快步伐。

第2期成员在实验室进行交流讨论

“很多同学认为设计CPU是一个极难的工作,事实证明本科生完全有能力完成。‘一生一芯一系统’是牵引学院教学改革的重要抓手,第一期的成功改变了学生重软件轻硬件的观念,提升了学生的计算机系统能力。我们这一项目最终的目的就是培养学生自主学习、问题解决、团队合作等一系列综合能力。”信息科学与工程学院党委书记陈文波说。

何安平坦言,第一期芯片研发比较保守,第二期、第三期会不断加大难度。“之所以以‘一生一芯一系统’命名,是为了先组织一部分同学参与到芯片设计项目,继而推广,让所有学生都能参与进来是我们的目标。”

2022级的新生杨延睿也加入到了“一生一芯一系统”第二期的研发中,参与一小部分设计工作。“学长学姐们的专业水平很高,和他们一起学习研讨,我的成长速度很快。”他希望,自己能够像他们一样,也做点了不起的事情,早日设计出属于自己的成果。

文字|法伊莎 王阳

图片|王阳

(兰州大学官方公众号)